Design a Full Adder Using a Suitable Multiplexer

In the combinational circuits, different logic gates are used to design encoder, multiplexer, decoder & de-multiplexer. These circuits have some characteristics like the output of this circuit mainly depends on the levels which are there at input terminals at any time. This circuit doesn't include any memory. The earlier state of the input doesn't have any influence on the current state of this circuit. The inputs and outputs of a combinational circuit are 'n' no. of inputs & 'm' no. of outputs. Some of the combinational circuits are half adder and full adder, subtractor, encoder, decoder, multiplexer, and demultiplexer. This article discusses an overview of half adder and full adder and it's working with truth tables.

What is an Adder?

An adder is a digital logic circuit in electronics that is extensively used for the addition of numbers. In many computers and other types of processors, adders are even used to calculate addresses and related activities and calculate table indices in the ALU and even utilized in other parts of the processors. These can be built for many numerical representations like excess-3 or binary coded decimal. Adders are basically classified into two types: Half Adder and Full Adder.

What is Half Adder and Full Adder Circuit?

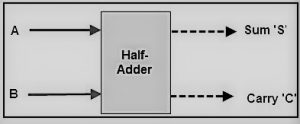

The half adder circuit has two inputs: A and B, which add two input digits and generates a carry and a sum. The full adder circuit has three inputs: A and C, which add three input numbers and generates a carry and sum. This article gives detailed information about what is the purpose of a half adder and full adder in tabular forms and even in circuit diagrams too. It is already mentioned that the main and crucial purpose of adders is addition. Below are the detailed half adder and full adder theory.

Half Adder

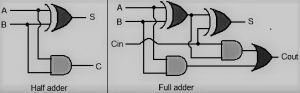

So, coming to the scenario of half adder, it adds two binary digits where the input bits are termed as augend and addend and the result will be two outputs one is the sum and the other is carry. To perform the sum operation, XOR is applied to both the inputs, and AND gate is applied to both inputs to produce carry.

Whereas in the full adder circuit, it adds 3 one-bit numbers, where two of the three bits can be referred to as operands and the other is termed as bit carried in. The produced output is 2-bit output and these can be referred to as output carry and sum.

By using a half adder, you can design simple addition with the help of logic gates.

Let's see an example of adding two single bits.

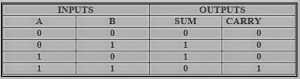

The 2-bit half adder truth table is as below:

0+0 = 0

0+1 = 1

1+0 = 1

1+1 = 10

These are the least possible single-bit combinations. But the result for 1+1 is 10, the sum result must be re-written as a 2-bit output. Thus, the equations can be written as

0+0 = 00

0+1 = 01

1+0 = 01

1+1 = 10

The output '1'of '10' is carry-out. 'SUM' is the normal output and 'CARRY' is the carry-out.

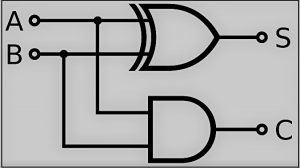

Now it has been cleared that a 1-bit adder can be easily implemented with the help of the XOR Gate for the output 'SUM' and an AND Gate for the 'Carry'.

For instance, when we need to add, two 8-bit bytes together, then it can be implemented by using a full-adder logic circuit. The half-adder is useful when you want to add one binary digit quantities.

A way to develop two-binary digit adders would be to make a truth table and reduce it. When you want to make a three binary digit adder, the half adder addition operation is performed twice. In a similar way, when you decide to make a four-digit adder, the operation is performed one more time. With this theory, it was clear that the implementation is simple, but development is a time taking process.

The simplest expression uses the exclusive OR function:

Sum= A XOR B

Carry = A AND B

And an equivalent expression in terms of the basic AND, OR, and NOT is:

SUM=A.B+A.B'

VHDL Code For Half Adder

Entity ha is

Port (a: in STD_LOGIC;

b : in STD_LOGIC;

sha : out STD_LOGIC;

cha : out STD_LOGIC);

end ha;

Architecture Behavioral of the above circuit is

begin

sha <= a xor b ;

cha <= a and b ;

end Behavioral

Half Adder IC Number

The implementation of half adder can be done through high-speed CMOS digital logic integrated circuits like 74HCxx series which includes the SN74HC08 (7408) & SN74HC86 (7486).

Half Adder Limitations

The main reason to call these binary adders like Half Adders is, that there is no range to include the carry bit using an earlier bit. So, this is a main limitation of HAs once used like binary adder particularly in real-time situations which involve adding several bits. So this limitation can be overcome by using the full adders.

Full Adder

This adder is difficult to implement when compared to half-adder.

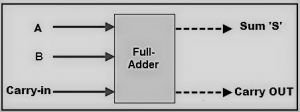

The difference between a half-adder and a full-adder is that the full-adder has three inputs and two outputs, whereas half adder has only two inputs and two outputs. The first two inputs are A and B and the third input is an input carry as C-IN. When a full-adder logic is designed, you string eight of them together to create a byte-wide adder and cascade the carry bit from one adder to the next.

The output carry is designated as C-OUT and the normal output is represented as S which is 'SUM'.

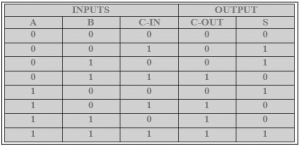

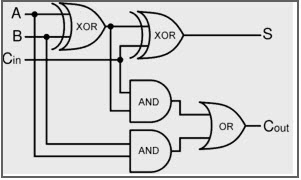

With the above full adder truth-table, the implementation of a full adder circuit can be understood easily. The SUM 'S' is produced in two steps:

- By XORing the provided inputs 'A' and 'B'

- The result of A XOR B is then XORed with the C-IN

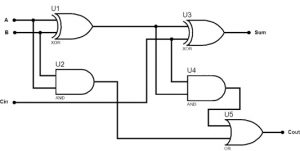

This generates SUM and C-OUT is true only when either two of three inputs are HIGH, then the C-OUT will be HIGH. So, we can implement a full adder circuit with the help of two half adder circuits. Initially, the half adder will be used to add A and B to produce a partial Sum and a second-half adder logic can be used to add C-IN to the Sum produced by the first half adder to get the final S output.

If any of the half adder logic produces a carry, there will be an output carry. So, C-OUT will be an OR function of the half-adder Carry outputs. Take a look at the implementation of the full adder circuit shown below.

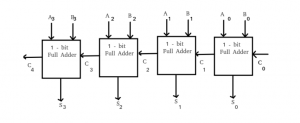

The implementation of larger logic diagrams is possible with the above full adder logic a simpler symbol is mostly used to represent the operation. Given below is a simpler schematic representation of a one-bit full adder.

With this type of symbol, we can add two bits together, taking a carry from the next lower order of magnitude, and sending a carry to the next higher order of magnitude. In a computer, for a multi-bit operation, each bit must be represented by a full adder and must be added simultaneously. Thus, to add two 8-bit numbers, you will need 8 full adders which can be formed by cascading two of the 4-bit blocks.

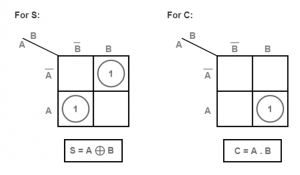

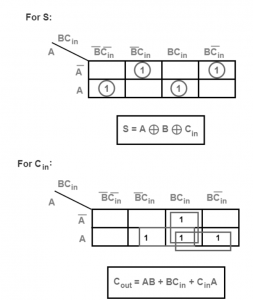

Half Adder and Full Adder using K-Map

Even the sum and carry outputs for half adder can also be obtained with the method of Karnaugh map (K-map). The half adder and full adder boolean expression can be obtained through K-map. So, the K-map for these adders is discussed below.

The half adder K-map is

The full adder K-Map is

Logical Expression of SUM and Carry

The logical expression of sum (S) can be determined based on the inputs mentioned in the table.

= A'B'Cin + A' B CCin' + A B'Cin'+ AB Cin

= Cin (A'B'+ AB) + Cin' (A'B +A B')

= Cin EX-OR (A EX-OR B)

= (1,2,4,7)

The logical expression of the carry (Cout) can be determined based on the inputs mentioned in the table.

= A'B Cin + AB'Cin + AB Cin' + ABCin

= AB + BCin + ACin

= (3, 5, 6, 7)

With the above-mentioned truth tables, the results can be obtained and the procedure is :

A combinational circuit combines the different gates in the circuit where those can be an encoder, decoder, multiplexer and demultiplexer. The characteristics of combinational circuits are as follows.

- The output at any instant of time is based only on the levels that are present at input terminals.

- It does not use any memory. The previous state of input does not have any effect on the present state of the circuit.

- It can have any number of inputs and m number of outputs.

VHDL Coding

VHDL coding for full adder include the following.

entity full_add is

Port ( a : in STD_LOGIC;

b : in STD_LOGIC;

cin : in STD_LOGIC;

sum : out STD_LOGIC;

cout : out STD_LOGIC);

end full_add;

Architecture Behavioral of full_add is

component ha is

Port ( a : in STD_LOGIC;

b : in STD_LOGIC;

sha : out STD_LOGIC;

cha : out STD_LOGIC);

end component;

signal s_s,c1,c2: STD_LOGIC ;

begin

HA1:ha port map(a,b,s_s,c1);

HA2:ha port map (s_s,cin,sum,c2);

cout<=c1 or c2 ;

end Behavioral;

The difference between half adder and full adder is that half adder produces results and full adder uses half adder to produce some other result. Similarly, while the Full-Adder is of two Half-Adders, the Full-Adder is the actual block that we use to create the arithmetic circuits.

Carry Lookahead Adders

In the concept of ripple carry adder circuits, the bits that are necessary for addition are immediately available. Whereas every adder section needs to hold its time for the arrival of carry from the previous adder block. Because of this, it takes more time to produce SUM and CARRY as each section in the circuit waits for the arrival of input.

For instance, to deliver output for the nth block, it needs to receive input from (n-1)th block. And this delay is correspondingly termed as propagation delay.

To overcome the delay in ripple carries adder, a carry-lookahead adder was introduced. Here, by using complicated hardware, the propagation delay can be minimized. The below diagram shows a carry-lookahead adder using full adders.

The truth table and corresponding output equations are

| A | B | C | C+1 | Condition |

| 0 | 0 | 0 | 0 | No Carry Generate |

| 0 | 0 | 1 | 0 | |

| 0 | 1 | 0 | 0 | |

| 0 | 1 | 1 | 1 | No Carry Propagate |

| 1 | 0 | 0 | 0 | |

| 1 | 0 | 1 | 1 | |

| 1 | 1 | 0 | 1 | Carry Generate |

| 1 | 1 | 1 | 1 |

The carry propagates equation is Pi = Ai XOR Bi and the carry generate is Gi = Ai*Bi. With these equations, the sum and carry equations can be represented as

SUM = Pi XOR Ci

Ci+1 = Gi + Pi*Ci

Gi delivers carry only when both the inputs Ai and Bi are 1 without considering the input carry. Pi is related to the carry propagation from Ci to Ci+1.

Difference between Half Adder and Full Adder

The difference between the half adder and full adder table is shown below.

| Half Adder | Full Adder |

| Half Adder (HA) is a combinational logic circuit and this circuit is used to add two one-bit digits. | Full Adder (FA) is a combinational circuit and this circuit is used to add three one bit digits. |

| In HA, once the carry is generated from the previous addition cannot be added to the next step. | In FA, once the carry is generated from the earlier addition, then it can be added to the next step. |

| Half adder includes two logic gates like AND gate and EX-OR gate. | Full adder includes two EX-OR gates, two OR gates, and two AND gates. |

| The input bits in the half adder are two like A, B. | The input bits in the full adder are three like A, B & C-in |

| Half adder sum and carry equation is S = a⊕b ; C = a*b | Full adder logic expression is S = a ⊕ b⊕Cin; Cout = (a*b) + (Cin*(a⊕b)). |

| HA is used in computers, calculators, devices used for digital measuring, etc. | FA is used in digital processors, multiple bit addition, etc. |

The key differences between the half adder and full adder are discussed below.

- Half adder generates sum & carry by adding two binary inputs whereas the full adder is used to generate sum & carry by adding three binary inputs. Both the half adder and full adder hardware architecture is not the same.

- The main feature that differentiates HA & FA is that in HA there is no such deal to consider the last addition carry like its input. But, a FA locates a particular input column like Cin to consider the last addition's carry bit.

- The two adders will show a difference based on the components used in the circuit for its construction. The half adders (HA's) are designed with the combination of two logic gates like AND & EX-OR whereas the FA is designed with the combination of three AND, two XOR & one OR gates.

- Basically, HA's operate on 2-two inputs of 1-bit, whereas the FA's operate on three inputs of 1-bit. Half adder is used in different electronic devices for evaluating the addition whereas the full adder is used in digital processors for the addition of a long bit.

- The similarities in these two adders are, both the HA & FA are combinational digital circuits so, they do not use any memory element such as sequential circuits. These circuits are essential for arithmetic operation to provide the addition of the binary number.

Full Adder Implementation using Half Adders

The implementation of a FA can be done through two half adders which are connected logically. The block diagram of this can be shown below which tells the connection of a FA using two half adders.

The sum and carry equations from previous calculations are

S = A' B' Cin + A' BC' in + ABCin

Cout = AB + ACin + BCin

The sum equation can be written as.

Cin (A'B '+ AB) + C 'in (A'B + A B')

So, Sum = Cin EX-OR (A EX-OR B)

Cin (A EX-OR B) + C'in (A EX-OR B)

= Cin EX-OR (A EX-OR B)

Cout can be written like the following.

COUT = AB + ACin + BCin.

COUT = AB + ACin+ BCin (A + ̅A)

= ABCin + AB + ACin + A' B Cin

= AB (1 + Cin) + ACin + A' B Cin

= A B + ACin + A' B Cin

= AB + ACin (B + B' ) + A' B Cin

= ABCin + AB + A'B Cin+ A' B Cin

= AB (Cin + 1) + A B Cin + A' B Cin

= AB + AB' Cin + A' B Cin

= AB + Cin ( AB' + A'B )

Therefore, COUT = AB + Cin (A EX-OR B)

Depending on the above two sums & carry equations, the FA circuit can be implemented with the help of two HAs & an OR gate. The circuit diagram of a full adder with two half adders is illustrated above.

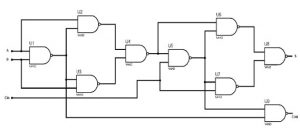

Full Adder Design with using NAND Gates

A NAND gate is one kind of universal gate, used to execute any kind of logic design. The FA circuit with the NAND gates diagram is shown below.

FA is an easy one-bit adder and if we desire to execute the addition of n-bit, then n no. of one-bit FAs must be employed in the cascade connection format.

Advantages

The advantages of half adder and full adder include the following.

- The foremost purpose of a half adder is to add two single-bit numbers

- Full adders hold the ability to add a carry bit which is the resulting from the previous addition

- With full adder, crucial circuits such as adder, multiplexer, and many others can be implemented

- The full adder circuits consume minimal power

- The advantages of a full adder over a half adder are, a full adder is used to overcome the drawback of a half adder because; half adder is mainly used to add two 1-bit numbers. Half adders don't add the carry bit, so to overcome this full adder is employed. In Full adder, the addition of three bits can be done and generates two outputs.

- Designing of adders is simple and it is a basic building block so that one-bit addition can be easily understood.

- This adder can be converted to half subtractor by adding an inverter.

- By using a full adder, high output can be obtained.

- High speed

- Very strong to supply voltage scaling

Disadvantages

The disadvantages of half adder and full adder include the following.

- In addition, half adder cannot use before carrying, so it is not applicable for cascading the addition of multi-bit.

- To overcome this drawback, FA is necessary to add three 1 bit.

- Once the FA is used in the form of a chain like a RA (Ripple Adder), then the drive capability of output can be decreased.

Applications

The applications of half adder and full adder include the following.

- The binary bits addition can be done by half adder using ALU within the computer because it uses adder.

- Half adder combination can be used for designing a full adder circuit.

- Half adders are used in the calculators and to measure the addresses as well as tables

- These circuits are used to handle different applications within digital circuits. In the future, it plays a key role in digital electronics.

- A FA circuit is used as an element in many large circuits such as Ripple Carry Adder. This adder adds the number of bits simultaneously.

- FAs are used in Arithmetic Logic Unit (ALU)

- FAs are used in graphics-related applications like GPU (Graphics Processing Unit)

- These are used in the multiplication circuit to execute Carryout Multiplication.

- In a computer, to generate the memory address & to build the program counterpoint toward subsequent instruction, the Arithmetic Logic Unit is used by using Full Adders.

Thus, whenever the addition of two binary numbers is done then the digits are added at first the least bits. This process can be performed through a half adder because the simplest n/w that allows adding two 1-bit numbers. The inputs of this adder are the binary digits whereas the outputs are the sum (S) & the carry (C).

Whenever the number of digits is included, then the HA network is utilized simply to connect the least digits, as the HA cannot add the carry number from the earlier class. A full adder can be defined as the base of all digital arithmetic devices. This is used for adding three 1-digit numbers. This adder includes three inputs like A, B, and Cin whereas the outputs are Sum and Cout.

Related Concepts

The concepts related to half adder and full adder just not stick to a single purpose. They have extensive usage in many applications and a few of the related are mentioned :

- Half adder and full adder IC number

- Development of 8-bit adder

- What are the half adder precautions?

- JAVA Applet of a Ripple Carry Adder

Therefore, this is all about the half adder and full adder theory along with the truth tables and logic diagrams, the design of full adder using half adder circuit is also shown. Many of the half adder and full adder pdf documents are available to provide advanced information of these concepts. It is furthermore important to know how a 4-bit full adder is implemented?

Design a Full Adder Using a Suitable Multiplexer

Source: https://www.elprocus.com/half-adder-and-full-adder/

0 Response to "Design a Full Adder Using a Suitable Multiplexer"

Post a Comment